기글 하드웨어 스페셜 게시판

2014년 7월에 펜티엄의 20주년 기념 모델인 펜티엄 G3258이 출시됐습니다. 여기에선 펜티엄 20년의 역사를 되돌아 보도록 하겠습니다.

등장했을 땐 별로 좋지 않았던 초기 펜티엄

초대 P5 코어 기반의 펜티엄이 나온 건 1993년의 일입니다.

펜티엄부터 펜티엄 MMX까지의 인텔 CPU 로드맵

펜티엄의 전 모델인 인텔 i486은 여러가지로 대성공한 CPU가 됐습니다. 그 전인 i386에서 무사히 32비트화가 이루어졌고, i286에 비해 크게 고속화하면서 i386은 제법 잘 팔렸으며 인텔의 경영 기반을 반석 위에 올리는 최초의 밑거름이 됐습니다. 다만 내부는 마이크로 코드를 여럿 사숑한 구성으로 속도와 전력 사용량을 개선할 여지가 많았으며 실제로도 AMD를 비롯한 경쟁사들은 이를 즉시 개량했습니다.

그래서 i486은 논리 회로를 소프트웨어가 아닌 하드웨어로 실현해 주요 명령을 1사이클 안에 실행할 수 있도록 개량했습니다. 또 파이프 라인의 고속화에도 신경을 써 프로세스의 미세화와 함께 100MHz로 구동하는 데 이르렀습니다.

허나 당시엔 경쟁 업체 역시 프로세스의 미세화 등으로 급속히 성능을 올려서 성능의 우위를 적극적으로 살리기엔 미묘한 점도 있었습니다. 이렇게 경쟁 업체와 성능 경쟁을 벌이던 1980년대 말에 설계가 시작된 것이 P5 코어입니다.

P5 코어의 초기 펜티엄

사실 P5 코어 개발이 시작됐을 때는 아직 CISC/RISC 논쟁은 결론을 내지 못했던 때였습니다. 1990년대에 들어서도 인텔 내부에서조차 CISC/RISC 중 어느 쪽이 유리한지 채 결론이 나오지 않았던 것입니다.

P5 코어 설계를 맡은 팀은 i486과 거의 같은 팀이며 i386과도 거의 같은 팀이기도 했습니다. 인텔 본사가 위치한 산타 클라라에 본거지를 두고 개발을 하던 이 팀은 x86을 버리지 않고 CISC를 기반으로 개발했습니다.

다만 단일 파이프라인 구조로는 더 이상 성능 개선을 전망할 수 없다 판단하고 2명령 슈퍼 스칼라 구성을 도입했습니다. 이 슈퍼 스칼라는 완전한 2명령 구성은 아닙니다. 파이프 라인은 U와 V의 2개인데 그 중에서 모든 명령을 실행할 수 있는 것은 U뿐이며 V는 사용 빈도가 높다고 판단하는 비교적 간단한 명령만 실행할 수 있는 구조입니다.

또 P5의 파이프 라인은 어디까지나 x86을 x86 명령으로 해석 및 실행하는 구조로서 당시에는 P6처럼 명령 변환이 포함되진 않았습니다. 이 비대칭 명령어 파이프라인은 나중에 출시되는 사이릭스의 M1같은 완전 대칭형 파이프라인과 비교해서 조잡한 점은 있지만, 최소한의 트랜지스터로 효과적인 성능을 내는 방법이었습니다.

이렇게 작은 명령의 처리 속도 개선과 FPU의 고속화, 데이터 버스 64비트화 등의 성능 향상을 위한 많은 개선이 이루어졌습니다. 그럼에도 불구하고 1세대의 펜티엄은 썩 좋은 결과를 보이지 못했는데요. 여기에는 이유가 몇가지 있습니다.

펜티엄이 별로였던 이유 1. 정수 연산 성능이 i486DX4보다 떨어짐

정수 연산 성능은 이론적으로 2명령/사이클 처리하니까 i486DX4/100MHz를 넘는 성능을 낼 수 있겠지만 실제 성능은 1.2~1.3명령/사이클에 머물러 절대적인 성능은 후기형 모델인 i486DX4/100MHz만 못한 경우가 있었습니다.

i486DX4

펜티엄이 별로였던 이유 2. 제 역할을 내지 못한 PCI

PCI을 적극 도입하기 위해 인텔 430LX(Mercury) 칩셋과 함께 출시했으나 이 PCI가 완전한 성능을 내지 못했습니다. 이 세대에선 아직 PCI의 스펙 자체가 정해지지 못한 것도 있고 호환성에도 문제가 있었습니다.

결과적으로 가장 안정적인(그리고 느린) 전송 방식이 사용되면서, 그 동안 계속 사용하며 성능 튜닝이 진행된 VL-Bus 접속의 디바이스보다 떨어지는 성능이 나오게 됐습니다.

펜티엄이 별로였던 이유 3. 비쌈

그리고 CPU 자체의 가격이 비쌌습니다. 초기 가격은 60MHz가 878달러, 66MHz가 964달러였습니다. 여기에 칩셋의 가격 또한 비싸다보니 CPU와 메인보드의 가격을 더하면 천오백달러 정도 되겠네요.

이와 대조적으로 1994년에 출시된 인텔 DX4는 100MHz가 580달러, 클럭이 다소 낮은 75MHz는 475달러였습니다. 칩셋도 SiS, OPTi/AMI 등의 써드파티 제품을 쓸 수 있었기에 CPU+메인보드의 가격을 천달러 이하로 낮추는 건 그리 어렵지 않았습니다.

인텔은 당초 펜티엄을 차세대 하이엔드 프로세서로 정하다보니 가격을 비싸게 잡은 것도 있습니다.

그런데 1993년엔 AMD와 사이릭스 같은 x86 호환 프로세서 업체의 추격 외에도 DEC의 알파나 IBM/모토로라의 파워PC, TI의 SuperSPARC+, MIPS의 R4200 처럼 펜티엄과 경쟁할 하이엔드 프로세서가 상당히 저렴하게 출시되던 시기였습니다.

그래서 인텔도 개선이 필요하다고 느꼈을 것입니다. 3월에는 제조 공정을 0.6μm의 BiCMOS로 미세화한 P54C 코어 펜티엄이 출시됩니다. 여기에 맞춰 칩셋도 새단장을 해 430NX(Neptune)을 거쳐 430FX(Triton)이 출시됩니다.

가격이 싸지면서 큰 인기를 누림. 버그가 등장해도 바로 수습

P54 코어를 사용한 펜티엄에 430FX 칩셋을 조합한 것이 이 시기의 하이엔드 PC 구성이었습니다. CPU는 처음에 849달러(90MHz)/995달러(100MHz)를 기록했으나 연말에는 가격이 절반 수준으로 급격히 떨어져 이제 컴퓨터를 구입한다면 DX4가 아니라 펜티엄이라는 분위기가 분명히 생기게 됩니다.

뒤이어 칩셋에서도 PCI 버스 마스터가 제대로 작동하게 되면서 VL-Bus보다 전체 성능이 높아졌습니다. 특히 그래픽카드에서 점차 PCI 대응이 늘어나면서 1995년에는 PCI 전용 가속 카드인 3dfx의 부두가 나오는 등 빠르게 보급됩니다.

직접 조립하는 사용자 사이에선 90MHz 버전(60MHz× 1.5배수)의 펜티엄을 구입해 100MHz(66MHz× 1.5배수)로 구동시키기 쉬우며, 운이 좋으면 75MHz 버전(50MHz× 1.5배수)에서 100MHz 구동 가능한 CPU를 뽑을 수도 있어 비교적 저렴하게 높은 성능을 내는 것도 가능했었습니다.

이후 매우 작은 값으로 나눗셈 연산을 하면 이상한 결과가 나온다는 펜티엄의 FDIV 버그가 나와 당시에는 큰 난리가 났으나 비교적 깔끔하게 수습했습니다.

그때는 FPU를 쓸 일은 거의 없으니까 버그가 있더라도 그만큼 싸게만 팔아달라고 말하는 사람들도 있었지만, 인텔이 전량 회수에 나서면서 그런 희망이 이루어질 일은 없었습니다.

버그가 있는 펜티엄을 집어 넣은 액세서리

또한 널리 알려지진 않았으나 P54C의 파생형 중에 P54CT라는 CPU가 있습니다. 이것은 듀얼 CPU 대응 제품으로 P54C와 P54CT를 1개씩 조합해 2 CPU의 SMP 구성이 가능하다는 것이 특징입니다. 즉 앞으로 나오게 될 제온 계열 서버/워크스테이션 제품의 조상이라 할 수 있겠습니다.

물론 메인보드도 2 CPU를 지원하는 것을 써야 했던지라 AMI의 Titan-II이나 타이얀의 Tomcat I 등이 출시됐습니다. 다만 하드웨어는 일단 논외로 치더라도 당시에 이걸 쓸 수 있었던 운영체제가 윈도우 NT 3.1과 일부 유닉스 계열 뿐인지라 그리 널리 쓰이진 않았습니다.

제조 공정 미세화가 추진된 2세대 펜티엄

P54C의 제조 프로세스를 0.35μm으로 전환한 것이 1995년에 등장한 P54CS 코어로 작동 클럭은 최대 200MHz에 달했습니다.

P54CS 코어 펜티엄

엄밀히 말하면 이 세대에는 P54CQS와 P54CS의 2가지 코어가 있었습니다. 둘 다 0.35μm CMOS로 제조하지만 P54CQS는 P54C와 다이 크기가 같은 156mm2, P54CS는 90mm2입니다.

이는 패키지의 관계에 따른 것으로서 P54CQS는 P54C와 같은 소켓t 5, P54CS는 소켓 7과 거의 비슷합니다. 거의 비슷하다고 말하는 이유는 54CQS의 다이 크기가 공식 확인되지 않았고 P54C와 마찬가지라고 했기 때문입니다. 다이 사이즈는 모르나 인터페이스는 다릅니다.

참고로 처음 출시된 건 P54CQS의 120MHz 버전이며 가격은 935달러였습니다. 3달 후에 발매된 133MHz 버전 역시 935달러이며 10월에는 모바일 120MHz가 681달러로 발매되는 등 가격이 꽤 빠르게 떨어졌습니다.

1996년 1월에는 150/166MHz 버전이 각각 547/749달러로 출시됐으며 이보다 클럭이 낮은 제품은 가격이 인하돼 구입 부담은 더욱 줄었습니다.

1997년에는 제조 공정을 유지하면서 MMX를 추가한 P55C가 펜티엄 MMX(정확히는 Pentium processor with MMX technologies)라는 이름으로 출시됩니다.

P55C MMX 펜티엄

달라진 점을 보면 MMX 유닛을 추가하고 파이프 라인을 1스테이지 늘렸습니다. 이 작업에 손을 댄 건 이스라엘 하이파에 설립된 디자인 센터로 그 팀을 지휘했던 사람은 인텔 사장까지 올랐던 Mooly Eden입니다.

또 펜티엄 MMX를 0.28μm CMOS로 미세화한 모델이 1997년 6월에 출시됐습니다. 이때는 이미 펜티엄 프로가 나온지라 펜티엄은 컨슈머 시장을 확대한다는 역할을 맡게 됐습니다.

펜티엄 프로

컨슈머용을 공략한다는 것 외에도 166MHz/200MHz의 펜티엄 MMX는 가격이 407/550달러라 초기 펜티엄과는 비교가 안 될 정도로 저렴해 인텔 의도와 정 반대로 사용자 층을 늘렸습니다.

왜 의도와 정 반대라 했냐면 인텔은 이 때 이미 펜티엄 2를 출시하기 시작했거든요. 허나 가격이 너무 비싸 매출이 벌로였습니다. 여기에 대해선 나중에 설명하겠습니다.

클래식 펜티엄의 마지막 제품은 0.25μm CMOS로 프로세스를 미세화된 Tillamook 코어입니다. 이 시기에 인텔은 이미 데스크탑용 펜티엄 2로 전환한다는 방침을 세웠는데요. 그 이유는 인텔 호환 CPU를 막기 위해서입니다.

P54CS 이후 줄곧 사용된 소켓 7를 호환 CPU 제조 업체 역시 이용했기에, 소켓을 바꾸지 않는 한 호환 CPU의 입지를 줄이기가 어려울 것이라고 인텔은 판단했습니다. 그래서 펜티엄 2에선 슬롯 1이라는 새로운 인터페이스를 도입했고 이와 동시에 슬롯 1을 특허로 보호해 호환 CPU 제조 업체으 사용을 막도록 했습니다.

슬롯 1을 쓴 펜티엄 2

다만 펜티엄 2을 바로 모바일에 쓰는 건 소비 전력에서 무리가 있다고 판단해 TCP(Tape Carriered Package)라는 기판에 직접 실장을 전제로 한 패키지 형태로 공급했습니다.

이 TCP의 펜티엄을 변환 기판에 붙여 여기에서 소켓 7의 변환 핀을 뽑아내는 라이저 카드가 대만에서 출시되거나, Tillamook 코어 기반이면서 임베디드 시장에 맞춰 소켓 7의 패키지 형태로 출시된 것이 조립 PC 시장에 나오긴 했지만, 그 수는 그리 많지 않았습니다.

인텔은 1998년 이후에 펜티엄 2에 주력했고 AMD와 사이릭스/IDT는 소켓 7에서 75/83/100MHz의 클럭을 내는 슈퍼 7을 내놓았지만, 사이릭스/IDT가 VIA에게 인수되고 AMD가 애슬론부터 슬롯 A로 건너감으로서 1999년 후반부터 급속히 소켓 7 시장이 축소됐고, P5로 시작된 펜티엄의 라인업은 2000년이 되서야 수습하게 됐습니다.

이 P5 코어는 이후에도 GPGPU인 라라비에서 한번 더 쓰였으며, 또 나이츠 코너도 대부분을 그대로 사용하고 제온 파이라는 이름으로 상품화됐습니다.

HPC를 위한 코프로세서 카드 제온 파이

그것과는 별도로 임베디드용 쿼크 X1000의 CPU 코어로 쓰이는 등. 여전히 펜티엄의 명맥은 이어지고 있습니다. 첫 출시 후 이미 21년이 지났음에도 불구하고 제품이 출시되고 있다는 점은 놀랍습니다.

P5와 함께 개발이 진행된 P6 마이크로 아키텍처

P5 코어의 개발과 병행해서 인텔 내부에선 P6의 개발을 시작했습니다. 개발을 시작한 건 1990년 6월이며 개발 거점은 오레건주에 위치한 디자인 센터입니다.

펜티엄 2부터 펜티엄 3까지의 인텔 CPU 로드맵

1990년은 아직 P5가 출시되기 전이며 i486이 나오던 시절입니다. 즉 P6과 P5는 개발 기간이 상당 수준 겹쳤던 것입니다.

P6은 초기 컨셉 단계에서 VILW를 비롯한 여러 방식을 검토했으며 이를 위해 DFA(Data Flow Analyzer)라 불리는 시뮬레이션 툴을 만들어 성능 테스트를 실시했습니다. 그 결과 슈퍼 스칼라+아웃 오브 오더 구성이 가장 성능이 높다는 결론을 낸 듯 합니다.

그런데 당시엔 슈퍼 스칼라에 관한 연구나 논문은 모두 RISC 프로세서를 기반으로 했으며 CISC로 아웃 오브 오더를 구현한 사례나 연구는 전무했다고 합니다.

그래서 프론트 엔드에서 x86의 CISC 명령을 RISC 식의 내부 명령으로 변환 처리한다는 아이디어가 등장합니다. 이러한 발상이 잘못된 것은 아닌 게 1993년에 알고리즘 개발이 시작된 AMD의 K5나 1993년에 출시된 NexGen의 Nx586이 모두 86 명령을 프론트 엔드에서 RISC 명령으로 변환하고 실행하는 방법을 구현했다는 것만 봐도 알 수 있습니다.

이들 회사들의 개발 시기를 생각하면 특정 회사의 방법을 다른 회사가 흉내낸 것이 아니라, 여러 회사들이 저마다 최적인 방법을 생각하다가 결국엔 모두 같은 결론을 냈다고 봐야 할 것입니다. 그리고 이 방식은 올바른 선택이었습니다.

P6 코어를 쓴 첫 프로세서. 펜티엄 프로의 탄생

최대 3명령 동시 인코딩, 최대 5명령 발행의 아웃 오브 오더 아키텍처 등, P5에 비해 매우 무거운 구성을 쓴 P6 코어의 첫 제품, 펜티엄 프로는 CPU 코어만 5.5만 개의 트랜지스터를 씁니다.

P6 코어를 처음으로 쓴 제품. 펜티엄 프로

이는 처음에 썼던 0.6μm BiCMOS 프로세스에서 306mm2에 이르기에 L2 캐시를 쓰기엔 크기가 너무 컸습니다. 그래서 L2 캐시는 다이 밖에 넣어야 했습니다.

L1 캐시만으로 그럭저럭 성능이 나온 P5와 대조적으로, P6 코어에서 L2 캐시를 빼면 성능은 크게 떨어집니다. 이는 코빙턴(Covington) 코어의 셀러론에서 증명됩니다.

따라서 L2 캐시를 탑재한 것은 정답이라 할 수 있으나 그때 당시엔 코어와 같은 속도로 작동하는 걸 중시하는 인텔이 처음으로 MCM(Multi-Chip Module) 패키징을 하는 것 자체가 큰 도전이었습니다. 그 결과 수율은 나빠졌고 제조 원가가 비쌀 수밖에 없었습니다.

그리고 150~200MHz의 클럭으로 작동했을 때 TDP는 31.7W(150MHz·256KB L2)~37.9W(200MHz·512KB L2)에 달합니다. 이는 펜티엄 MMX 233MHz의 TDP(17W)의 배 이상 숫자니 쿨링까지 신경써야 했습니다.

큰 다이와 독립된 L2 캐시를 사용하니 가격이 저렴할 리도 없고, 1993년 11월에 발표했을 때는 가장 싼 150MHz 버전이 974달러, 200MHz+512KB L2 버전은 1989달러의 어마어마한 가격에 팔렸습니다. 이러니 컨슈머용이라 부를 순 없었지요.

또 실제로 벤치마크를 하면 32비트 명령은 빨랐으나, 당시 주류였던 윈도우 95에선 오히려 펜티엄보다 떨어지는 결과가 나왔습니다. 이것은 윈도우 95의 상당 부분이 16비트 명령으로 쓰여졌으며 펜티엄 프로는 16비트로 최적화가 제대로 되지 않았기 때문입니다.

결과적으로 펜티엄 프로는 컨슈머 시장에 거의 보급되지 않았습니다. 반면 출시 당초부터 멀티 프로세서를 지원하고 정품 칩셋에서 최대 4P, 서드파티(서버웍스)가 만든 칩셋에서는 6P나 8P 구성이 가능했습니다.

OS도 윈도우 NT 서버를 비롯한 몇몇 OS가 SMP(대칭형 다중 프로세싱)를 지원해 빠르게 시장 점유율을 높이면서 RISC 기반의 서버에서 시장을 점점 빼앗을 수 있었습니다.

펜티엄 프로는 프로라는 이름에 걸맞게 엔터프라이즈와 서버 시장에서 확실히 보급됐습니다. 이를 감안하면 펜티엄 프로는 성공한 제품이라 해도 문제 없을 것입니다.

성능에서도 처음에는 0.6μm 프로세스를 쓰다가 나중에 0.35μm의 CMOS 프로세스로 바뀌고 최대 1MB의 L2 캐시를 갖춘 제품도 추가됐습니다.

AMD의 K6에게 추격당하는 펜티엄 2

펜티엄 프로의 후속작이 1997년에 발매된 카트마이(Klamath) 코어의 펜티엄 2입니다. 앞서 설명대로 인텔은 호환 업체를 떨어트리기 위해 소켓 7의 단종을 계획하고 있었습니다.

그래서 P6 코어를 컨슈머용으로 출시하기로 했습니다. 0.6μm 공정에서는 306mm2로 거대했던 P6 코어도 0.35μm 공정에서는 203mm2로 상식적인 크기로 들어오기에 불가능한 일은 아니었습니다. 또 MMX 명령어 셋트를 추가하고 16비트 명령 처리 속도를 높이면서 펜티엄과 비교해도 성능에서 개선이 명확해졌습니다.

소켓 7 대신 슬롯 1을 사용한 펜티엄 2

문제는 L2 캐시입니다. 펜티엄 프로와 같은 풀 스피드 오프 칩 L2 캐시는 제조 원가를 너무 많이 잡아먹기에 펜티엄 2는 카트리지 내부에 하프 스피드로 작동하는 SRAM 칩을 CPU와 함께 탐재하는 방식으로 전환했습니다.

속도가 절반인 대신 용량은 512KB로 늘어났기에 캐시에서 큰 성능 저하는 발생하지 않았고 제조 원가를 억제할 수 있었으니 이는 타당한 방법입니다. 허나 가격을 억제했다고는 해도 233MHz가 636달러, 300MHz는 1981달러로 여전히 비싼 가격인지라 컨슈모 시장에서 보급은 썩 빠르진 못했습니다.

이런 추세가 변하는 것은 1998년에 0.25μm 프로세스로 이행하면서부터입니다. 우선 1월 말에 66MHz 기반의 333MHz 버전이 나오는데 이건 722달러였습니다. 이와 더불어 기존 제품의 가격 인하도 이어졌습니다.

그리고 4월 14일에는 100MHz FSB의 350/400MHz 버전이 각각 621/824달러로 기존에 비해 훨씬 저렴한 가격에 출시됐으며, 셀러론 266Mhz가 155달러로 판매됐습니다. 이는 AMD에 의한 급속한 추격에서 비롯된 점이 큽니다.

AMD는 NexGen의 Nx686을 바탕으로 K6을 1997년 4월에 발표합니다. 처음엔 233MHz에 그쳤지만 1998년에는 0.25μm로 미세화한 Little Foot 코어로 전환해 300MHz대로 클럭을 높였습니다. 또 K6-2가 1998년 5월에 출시돼 최대 350MHz까지 높였습니다.

저렴한데다 기존의 소켓 7에서 작동해 인기를 얻은 AMD-K6

K6/K6-2는 부동 소수점 연산은 몰라도 정수 연산은 펜티엄 II와 동등하며 5월에 출시된 K6-2 300MHz는 281달러로 가격은 훨씬 쌌습니다.

슈퍼 7 외에 기존의 66MHz FSB 기반 소켓 7에서도 작동하면서 슬롯 1의 펜티엄 2보다 훨씬 싸게 구입 가능하니, 가격 경쟁력이 인텔을 크게 앞설 수밖에 없었고 이쯤 되면 인텔은 가격을 낮춰 맞서지 않을 수가 없었습니다.

인텔은 셀러론으로 이 차이를 메꿀 생각이었으나 L2 캐시를 생략하면서 성능은 떨어졌습니다. 다만 100MHz FSB의 400MHz로 오버클럭해도 별 문제 없이 작동했기에 DIY 사용자들은 상대적으로 저렴하다고 여겨 묘한 인기를 누렸으나 K6-2에 대항할 수 있는 레벨은 아니었습니다.

L2 캐시를 내장한 펜티엄 3

이런 점에서 인텔은 차세대 제품의 개발을 서둘렀습니다. 그것이 SSE을 탑재하고 함께 파이프라인을 1스테이지 늘려 고속화한 카트마이(Katmai) 코어의 펜티엄 3입니다.

펜티엄 3

경쟁 상대인 AMD K6-2는 350MHz까지 올라갔습니다. 뒤이어 나온 K6-III는 대용량 캐시가 발목을 잡으면서 450MHz도 겨우 도달한 수준이라 600Mhz까지 올리기엔 시간이 더 필요할 것이라 판단했던 듯 합니다.

경쟁이 심해지면서 처음 발표된 450/500MHz의 가격은 각각 469/696달러, 5월에 출시된 550MHz도 744달러로 다소 저렴한 편이었습니다.

우선 펜티엄 2 시절부터 서버/워크스테이션용으로 2P 이상의 동작을 보장한 제품을 펜티엄 2 제온/펜티엄 3 제온이라고 내놨는데, 이 쪽은 여전히 비싼 가격을 자랑했던지라(펜티엄 3 제온은 500MHz에 L2 512KB/1MB/2MB에 따라 각각 931/1980/3692달러) 컨슈머용 펜티엄 2/3의 가격이 어느 정도 떨어지는 건 시간이 좀 더 걸렸습니다.

카트마이 코어의 펜티엄 3는 AMD 애슬론의 맹추격을 맞게 됩니다. 1999년 6월에 발표된 AMD의 K7 애슬론은 같은 클럭으로 작동하는 펜티엄 3보다 약간 싼 정도로 나왔습니다(당시 일본에서 출시 가격은 500/550/600MHz가 각각 42120엔, 62270엔, 90870엔).

처음엔 메인보드를 구하기도 힘들고 비싸기도 했으나 2000년대에 들어서면서 이것도 거의 해결됐습니다. 또 파이프라인 구조적으로 K7이 클럭을 높이기가 쉬워 마지막엔 K7 코어에서 700MHz를 찍어 인텔을 따라잡게 됩니다.

카트마이 코어의 펜티엄 3. 펜티엄 2와 마찬가지로 기판 위에 CPU 코어와 512KB의 L2 캐시를 따로 구현했습니다.

AMD에 맞서 인텔은 0.18μm로 미세화한 코퍼마인(Coppermine) 코어의 펜티엄 3를 1999년 말에 출시합니다. 코퍼마인에서는 제조 공정 미세화 덕분에 다이 크기에 여유가 생기면서 L2 캐시를 마침내 다이 내부에 통합하는 게 가능해졌습니다.

코퍼마인 코어의 펜티엄 3. L2 캐시를 CPU에 내장

이는 갑작스런 일은 아닙니다. 사실 처음에 L2 캐시를 통합한 건 1998년에 출시된 멘도시노(Mendocino) 기반의 셀러론입니다.

셀러론 정도의 등급에서 L2 캐시를 따로 넣으면 제조 원가가 너무 비싸지기에 수지가 맞지 않습니다. 그런데 L2 캐시가 없으면 성능이 낮습니다. 그래서 모바일 펜티엄 2용으로 제조 프로세스를 약간(0.25μm → 0.22μm) 미세화하고 그만큼 L2 캐시를 칩 내부에 통합한 Dixon 코어를 데스크탑용에서 멘도시노란 이름으로 출시한다는 모험을 벌인 것입니다.

L2 캐시가 128KB로 줄었기에(Dixon은 256KB) 성능은 약간 낮았지만 그래도 풀 스피드로 동작하는 만큼 코빙턴에 비해 성능 개선은 눈부신 수준이었습니다. 또 제조 공정의 미세화 덕분에 빠른 클럭으로 동작했습니다.

그래서 당시의 조립 PC에선 멘도시노 코어의 셀러론 300A MHz를 구입해 100MHz FSB로 설정해서 450MHz의 오버클럭을 하는 게 유행이었습니다. 발열이 늘어나면서 히트싱크를 교환해야 했지만 그래도 펜티엄 3 450MHz보다는 훨씬 쌌습니다.

셀러론 300A

이야기를 되돌려서 L2 캐시를 온 다이에 통합하자 슬롯 1같은 거대한 패키지가 필요없게 됐습니다. 그래서 인텔은 새로 소켓 370을 내놓습니다. 말 그대로 370핀 PGA 패키지로 슬롯 1에 비해 실장 면적은 물론 제조 원가도 낮출 수 있었습니다.

소켓 370. 슬롯 1에 비해 실장 면적과 제조 원가를 크게 줄일 수 있었습니다.

이와 함께 코퍼마인에선 큰 폭의 가격 인하가 이뤄져 AMD와의 경쟁에서 우위를 차지하고자 했으나, AMD도 똑같이 0.18μm로 미세화(K7.5코어) 작업을 1999년에 도입하고 2000년 6월에는 L2 캐시를 다이에 내장한 썬더버드 코어를 출시하면서 가격에서도 인텔보다 약간 싼 수준을 유지, 인텔은 AMD의 견제에 실패했습니다.

오히려 클럭 1GHz 버전을 먼저 내놓으며 1GHz 경쟁에서 앞섰던 AMD와 달리(며칠 차이긴 하지만), 인텔은 코퍼마인 코어의 펜티엄 3가 1.13GHz의 리콜 사태까지 벌어지면서 AMD에게 완전히 추월당하게 됩니다.

코퍼마인 코어의 펜티엄 3

다행히도 인텔은 펜티엄 3와 함게 P4 코어를 개발하고 있었으며, 데스크탑과 서버용으로 P4 코어를 전면 출시하기로 결심했습니다.

이와 함께 0.13μm 프로세스로 미세화한 투알라틴(Tualatin)은 일부 서버 및 조립 시장에 출시하기도 했고, P4가 모바일용으로 쓰기엔 소비 전력이 너무 크다보니 펜티엄 M이 등장하는 2003년까진 계속 쓰였습니다. 첫 등장 후 8년 동안 계속 쓰였으나 상당히 오랬동안 쓴 제품입니다.

또 펜티엄 M이나 그 뒤를 이은 코어 마이크로 아키텍처는 어떤 의미에서 P6의 발전 확장형이며 지금도 계속 쓰이는 아키텍처라 해도 틀리지 않습니다.

펜티엄의 인기를 단번에 끌어올린 펜티엄 4

P6 코어 개발보다 다소 늦게 오레건에서 펜티엄 4의 개발을 시작했습니다. 설계 팀은 분명하지 않으나 산타 클라라에 있는 인텔 본사 설계팀이 오레건으로 장소를 옮겼던 것으로 보이며 P5의 설계 팀 멤버 중 적잖은 수가 펜티엄 4에 참여했습니다. 이 점에 대해선 The Pentium Chronicles에도 별로 자세한 이야기는 나오지 않았습니다.

펜티엄 4 세대의 인텔 CPU 로드맵

처음 발표된 것이 윌라멧(Willamette) 코어의 펜티엄 4이며 이는 2000년 말에 있었던 일입니다. 출시 초기의 클럭은 1.4GHz와 1.5GHz로 다소 낮았으나 다음해인 패키지를 바꾸면서 최대 2GHz까지 동작 클럭을 높였습니다.

윌라멧 코어의 초기형 펜티엄 4

펜티엄 4의 설계 목표는 당연히 P6의 후속작인 만큼 P6을 넘는 성능을 내는 게 필수였습니다. 결과적으로 아웃 오브 오더와 슈퍼 스칼라, CISC→ RISC 변환같은 P6의 특징을 그대로 계승한 셈인데, 이를 그대로 쓰면 P6과 다를 게 없습니다.

그래서 펜티엄 4는 어찌됐던 동작 클럭을 높이는 쪽으로 아키텍처를 바꾸게 됐습니다. 이는 P6에서 IPC를 높이는 방향으로 회로를 바꾸자 다이 크기가 커져 L2 캐시를 다이 내부에 넣지 못했던 데에 따른 교훈에서 나온 것이지 싶습니다.

IPC를 높이면 필연적으로 트랜지스터 수가 늘어나지만 그렇게 해도 성능 향상은 트랜지스터 증가 폭의 제곱근 정도밖에 안 된다. 바로 이 폴락의 법칙이 발표된 게 1999년의 일입니다. 인텔 내부에선 당연히 이걸 알고 있던 듯 합니다.

1999년 11월에 개최된 ACM/IEEE International Symposium on Microarchitecture 32(Micro32) 기조 강연에서 인텔의 Fellow를 맡았던 Fred Pollack가 제시한 슬라이드. 이후 폴락의 법칙으로 알려지게 됩니다.

만약 P6의 2배에 달하는 성능을 같은 클럭으로 실현한다면 대충 계산해도 트랜지스터 수는 4배가 되며 다이 크기는 4배까진 아니더라도 3배 이상이 될 수 있습니다. 그럴 바에야 IPC는 P6 수준으로 낮추고 클럭을 높이는 게 더 낫다고 판단해도 잘못된 건 아닙니다.

P4의 개발이 시작된 1990년대 후반에는 아직 프로세스 미세화나 고성능/전력 절약화의 한계가 확실하게 보이지 않았던 시기입니다. 열 밀도가 이대로 높아지면 태양 표면보다 뜨거워질 것이란 이야기가 나오고 있긴 했지만, 거꾸로 말하면 그거 말곤 저해 요인이 없었다는 것입니다. 따라서 기본적으로는 프로세스 미세화를 믿고 동작 클럭을 높이는 방향으로 아키텍처를 바꿨다고 한들 이상하지 않습니다.

동작 클럭을 대폭 끌어올린 펜티엄 4의 구조

방향이 결정됐으니 다음은 어떻게 구현하느냐입니다. CPU의 파이프라인에서 가장 시간이 걸리는 건 사실 명령의 디코딩입니다. 그래서 펜티엄 4는 대담하게도 CPU의 파이프라인에서 명령 페치와 복호화를 분리했습니다. 이 페치/디코드는 CPU의 처리 파이프라인과는 독립적으로 움직이게 됐습니다.

여기에서 페치/디코드와 그 뒤를 잇는 수행 사이에 끼는 것이 추적-트레이스- 캐시입니다. 추적 캐시는 디코딩과 CISC→ RISC 변환이 끝난 내부 명령 상태-스테이트-를 최대 1만 2000개 저장할 수 있어, 실행 파이프가 디코딩의 발목을 잡지 않도록 고안했습니다.

또 고속화를 위해 실행 단계를 20스테이지의 긴 파이프라인으로 분할했는데, 이렇게 하면 스케줄러에서 큐를 잡기가 어려워집니다. 이 때문에 큐의 깊이는 적당히 넣고 실행 유닛을 많이 넣을 필요가 없다고 해서 ALU(Arithmetic Logic Unit:연산 장치)는 2유닛밖에 없습니다.

다만 여기에서도 ALU의 폭을 16비트로 제한하고 대신 두배의 속도로 동작하게 해 이용 효율을 개선하는 등의 수정도 더했습니다. 다만 그래도 실행 유닛의 이용 효율을 높이기 어렵다는 건 인텔도 알고 있었으며, 그래서 처음부터 멀티스레딩 기능(하이퍼 스레딩)을 넣고 초기엔 이를 무효화하는 식으로 출시했습니다.

결과적으로 같은 0.18μm 프로세스를 사용한 코퍼마인 코어의 펜티엄 3가 1.13GHz이 끝인데 비해, 윌라멧 기반의 펜티엄 4는 2GHz, 0.13μm 프로세스 세대의 튜알라틴-S 펜티엄 3가 1.4GHz로 동작한데 비해 노스우드 기반에선 3.4GHz까지 동작 클럭을 높일 수 있었습니다.

노스우드 코어의 펜티엄 4

물론 절대 성능을 따지면 펜티엄 4는 같은 클럭으로 작동하는 펜티엄 3만 못합니다. 하지만 그걸 보충하고도 남을 정도로 동작 클럭이 높아지면서 AMD의 애슬론 계열과 경쟁할만한 성능을 내게 됐습니다.

펜티엄 4의 발목을 잡은 램버스 DRDRAM

이야기를 되돌려서 2000년 말에 펜티엄 4는 우선 소켓 423 패키지로 출시됐습니다. 당시 인텔은 램버스와의 계약 관계로 램버스 기반의 DRDRAM을 쓰지 않으면 안 됐습니다. 그런데 이것이 성능과 가격에서 발목을 잡았습니다.

초기 펜티엄 4의 소켓 423

DRDRAM은 펜티엄 3 세대부터 도입했습니다. 허나 최대 전송 속도 1.6GB/초가 나오는 PC800 DRDRAM을 사용하는 것보다 최대 전송 속도가 1.066GB/초가 나오는 PC133 SDRAM을 사용하는 것이 성능이 더 나오는 신기한 현상이 있었습니다.

이후 램버스 관계자가 말하기로는 "DRDRAM이 전송 속도가 빠르지만 레이턴시는 크기에, 단순히 칩셋의 메모리 컨트롤러가 DRDRAM을 지원하는 것만으론 제 성능을 낼 수 없고, CPU의 메모리 로드/스토어 유닛이 처음부터 메모리 레이턴시가 크다는 걸 상정해서 파이프라인 동작을 하지 않으면 제 성능을 내지 못함"이라고 합니다.

펜티엄 3는 설계 당시에 그런 최적화가 없었지만 펜티엄 4는 이 점을 나름 배려해서 만들었기에 펜티엄 4에선 DRDRAM이 제 성능을 낼 수 있다는 설명이었지만 실제로 제 성능을 낼 수 있었을지를 생각하면 의심스러운 점이 있습니다.

거기에 DRDRAM의 가격이 급등한데 이어 실제로 800MHz에서 구동할 수 있는 제품은 적었고 600MHz/700MHz로 작동하는 PC600과 PC700의 유통량이 많았습니다. 그 결과 PC800 메모리의 조합까지 더하면 경쟁 상대인 애슬론에 비해 훨씬 비쌀 수밖에 없었습니다.

또 당시부터 펜티엄 4의 소비 전력은 엄청 높은 편이었으며 이 때문에 새로운 ATX 12V 파워가 책정돼 이 또한 비용 상승에 기여했습니다. 다행인지 불행인진 모르겠으나 이를 조금이라도 커버하기 위해 Direct RDRAM에 트랜스레이터(MTH:Memory Translator Hub)을 넣어 PC100 SDRAM을 쓸 수 있도록 고안했는데, 이 MTH가 몇번이나 다시 만들었음에도 불구하고 안정화되지 않아 결국 리콜되는 일도 있었습니다.

한편 인텔 이외의 업체는 모두 DDR-SDRAM을 지향하여 결국엔 펜티엄 4용 DDR-SDRAM 대응 호환 칩셋이 나오기까지 이르렀고, 인텔은 결국 방향을 전환해 램버스와 계약을 파기하고 DDR-SDRAM을 지원하는 칩셋을 직접 내놓게 됐습니다.

이로써 펜티엄 4도 쓸데없는 핸디캡이 사라졌으며 이후엔 순조롭게 제품을 내놓았습니다. 허나 AMD도 애슬론 XP의 성능이 다소 둔화되면서 이를 해결하기 위해 2002년 10월에 AMD가 해머(Hammer) 코어의 애슬론 64를 내놓자 펜티엄 4는 다른 방도를 내놓게 됩니다.

그래서 2003년 4월에 펜티엄 4 HT, 하이퍼스레딩의 활성화와 DDR-400 메모리의 지원을 서두르게 됩니다. 다행히 AMD는 130nm SOI 프로세스에서 크게 비틀거리며 제품이 제대로 나오기까지 사실상 1년 정도 늦어졌고 인텔의 이러한 행보는 기우에 그치게 됐습니다. 그러나 다음 세대에선 인텔도 다시 수렁에 빠지게 됐습니다.

하이퍼스레딩을 활성화한 펜티엄 4 HT. 3.06GHz 이상의 펜티엄 4는 모두 하이퍼스레딩을 지원합니다.

펜티엄 4 세대의 인텔 CPU 로드맵

높은 소비 전력이 문제가 된 프레스컷

2004년에 출시된 프레스컷은 31 스테이지 파이프라인을 가진 신제품입니다. 가장 큰 특징은 64비트의 지원, 가상화, 보안 기능 등입니다.

90nm 세대의 프로세스 P1262를 채용한 프레스컷

게다가 이것도 스펙이 정해지기 전에 구현해야 하는 어려운 상황이었습니다. 그래서 인텔은 기존의 펜티엄 4 파이프라인에 일종의 마이크로 코드와 디코더를 추가하는 방법을 선택했습니다.

기본적으로 페치/디코드 자체는 바뀌지 않았지만 프레스컷 세대에선 내부 RISC 명령 자체보다는 내부 RISC 명령에 대한 포인터가 들어갔다고 할 수 있겠습니다.

실행 파이프라인은 그 포인터를 받아 현재의 동작 모드에 맞춰 명령을 마이크로 코드에서 꺼내 처리합니다.

보통 마이크로 코드를 이용하면 그 명령만 레이턴시가 수십 사이클까지도 달하지만 프레스컷은 이 마이크로 코드 액세스를 파이프라인화해 1사이클 안에 처리할 수 있도록 만들었습니다. 이건 멋진 것이죠.

다만 추가된 11 스테이지 파이프라인은 고속화에 전혀 기여한 게 없습니다. 이를 커버하기 위해 LVS라는 새로운 회로 구동 방식을 도입했으나 그 결과은 안정적으로 동작하지 못하는 높은 소비전력으로 이어졌습니다.

펜티엄 브랜드의 종말

결국 인텔은 프레스컷 세대에서 동작 클럭을 높이는 걸 단념하고, 대신 2개의 코어를 MCM(Multi-Chip Module) 구조로 조합하는 펜티엄 D를 내놓게 됩니다.

당시엔 AMD가 빠르게 프로세스를 개선한 시기라서, 듀얼코어 애슬론 64 X2는 펜티엄 D에 비해 성능이 높고 소비 전력도 낮았으며 가격도 그리 비싸지 않았습니다. 덕분에 AMD는 급격히 시장 점유율을 높였고 당연히 인텔의 점유율은 그만큼 줄어들었습니다.

이를 커버하기 위해 2005년에는 L2 캐시를 2MB까지 늘린 프레스컷(Prescott-2M)을 투입하고, 이듬해인 2006년에는 65nm 공정으로 미세화한 시더밀(CederMill) 코어의 펜티엄 4를 넣었으며 이를 멀티 코어 구조화한 프레슬러(Presler) 코어의 펜티엄 D도 출시합니다.

이 2005~2006년엔 뒤떨어지는 성능과 소비 전력을 가격과 스펙 차이로 커버한다는 전략을 펴면서, 세세한 스펙을 바꾼 펜티엄 4를 30종류 이상 시장에 출시해 인텔 직원조차 모델 번호를 물어봐도 스펙이 제대로 생각나지 않는다는 일까지 벌어지기도 했습니다.

제품의 매력을 급격하기 끌어 올릴 마법은 없습니다. 마케팅에선 일단 손에 들고 있는 무기로 싸울 수밖에 없으니 이러한 라인업 확충은 부득이한 것이나, 그 결과 브랜드 가치가 떨어졌습니다.

안 그래도 열세에 처했는데 이렇게 저렴하게 팔기 시작하면서 이제는 펜티엄이라는 브랜드 자체가 저가형이 됐다고 인식하게 되는 것도 어쩔 수 없는 일일 것입니다.

이를 대체하는 형태로 시장에 등장한 콘로(Conroe) 계열 제품이 코어 2라는 브랜드를 붙인 것도 어떤 의미에서는 당연한 것입니다. 결국 펜티엄 4/D의 판매 종료와 맞춰 펜티엄이라는 브랜드도 일단락을 맞이하게 된 것은 어쩔 수 없는 일입니다.

빛을 보지 못했던 전설 속의 CPU. Timna

앞에선 P6 대신 P4가 메인스트림에 제공된 역사를 설명했는데, 이 시기 교체의 그늘 뒤에 가려졌던 프로젝트가 하나 있었습니다.

인텔은 일찌기 셀러론의 제품 라인업을 강화해 저렴한 가격에 내놓겠다는 의도로 카트마이 기반의 펜티엄 3 코어에 인텔 752 기반 그래픽, 그리고 MCH까지 하나의 칩으로 통합한 제품을 개발했는데 이것이 바로 팀나(Timna)입니다.

펜티엄 2부터 펜티엄 3까지의 인텔 CPU 로드맵

팀나는 Direct RDRAM 메모리를 쓰기로 계획했는데 이것이 셀러론 치고는 너무 비싸다는 논란이 있었습니다. 그래서 MTH(Memory Translator Hub를 사용해 PC100 SDRAM을 사용할 수 있도록 연구했지만 다음엔 MTH에 문제가 생기면서 어려워졌습니다. 결국 인텔은 팀나 그 자체를 취소했습니다.

인텔의 흑역사 중에서도 유명한 편인 Timna. 2009년 봄 IDF에서 당시 엘버트 유모 수석 부사장이 선보였던 것입니다.

팀나의 설계에 참여했던 곳은 펜티엄 MMX를 개발했던 이스라엘 하이파의 설계 팀입니다. 이곳은 팀나를 중단하고 그 대신 새로운 CPU 코어인 바니아스(Banias)의 설계에 뛰어듭니다.

이 하이파 설계팀은 팀나를 개발할 때 오레건 팀과 긴밀하게 연락을 주고받아 카트마이를 독자적으로 0.18μm 공정화했습니다. 코퍼마인을 기반으로 한 것은 아니며 자체 개량이나 변경이 들어갔습니다. 파이프라인 그 자체를 재검토하는 변경은 없었다고.

이 경험 그대로 바니아스에 이어졌습니다. 펜티엄 4는 소비 전력이 상당히 높아질 가능성이 있었습니다. 실제로 모바일 펜티엄 4-M과 모바일 펜티엄 4도 출시했는데 각각 TDP가 26~35W, 60~88W로 높았습니다.

크기가 큰 노트북이라면 어떻게든 모바일 펜티엄 4-M을 쓸 수 있었으나, 모바일 펜티엄 4는 데스크탑, 혹은 DTR(DeskTop Replacement)라고 불리는 노트북 2대 쯤에 해당하는 물건에 쓰이는 데 그쳤습니다.

그러다보니 데스크탑에선 펜티엄 4로 바뀌어도 노트북에선 오랬동안 모바일 펜티엄 3가 쓰였는데요. 바니아스는 이를 대체하는 것을 목표로 설계됐습니다.

성능/소비 전력을 중시한 바니아스

펜티엄 M 세대의 인텔 CPU 로드맵

바니아스의 파이프라인은 펜티엄 3까지 쓰인 P6 아키텍처와 큰 차이는 없습니다. 실행 유닛 그 자체는 대응 명령이 늘어나는 등 강화된 점이 있으나 프론트엔드까지의 구조 자체는 거의 같습니다.

바니아스에선 절대적인 성능 개선은 크게 실현하지 않았습니다. 동작 클럭도 다소 개선됐으나 0.13μm에서는 투알라틴-S가 1.4GHz던 것이 바니아스에선 1.7GHz가 된 것 정도니 파이프라인의 경로를 개선한 수준에 그쳤다 할 수 있습니다.

바니아스의 다이

그 대신 바니아스에선 성능/전력 비율을 중시했습니다. 이는 모바일임을 감안하면 당연한 이야기입니다. 그래서 도입한 것이 클럭 게이팅(Clock Gating)에 의한 전력 절약 관리입니다.

지금은 당연해진 클럭 게이팅이지만 당시에 컨슈머 CPU에서 이를 구현한 것은 바니아스 뿐이었습니다. 이것은 회로를 잘게 나눠 불필요한 그룹에 클럭 신호를 공급하지 않는 구조입니다.

클럭 게이팅을 지원하는 로직 회로. 왼쪽 위 Latch에 이어지는 클럭에 스위치가 있으며, 적색 테두리 안에 클럭이 공급됩니다.

CMOS의 소비 전력은 패시브와 액티브로 나눌 수 있습니다. 패시브는 누설 전류에서 비롯된 것으로서 클럭 게이팅으로 줄일 순 없습니다(이걸 줄이는 것이 파워 게이팅입니다).

반면 액티브는 클럭에 비례하는 형태로 늘어나는데 기존에는 사용되지 않는 부분(정수 연산 중에 쓰이지 않는 부동소수점 유닛이라던가)에도 무조건 클럭 신호가 공급되면서 이것이 소비 전력을 끌어올린 이ㅠ가 됐습니다.

클럭이 공급되지 않으면 이 부분의 소비 전력이 줄어듭니다. 허나 소비 전력이 줄어든다고 간단하게 말할 수 있으나 도입은 쉽지 않습니다. 원래 CPU는 액티브 회로라 해서 CPU 클럭 신호가 어느 정도 이상 있는 걸 전제로 깔고 구성되기 때문입니다. 인텔 스피드 스텝(SpeedStep)과 AMD 파워나우(PowerNow!)에서 최저 클럭이 정해진 것도 다 이것 때문입니다.

하지만 클럭 신호를 완전히 끊어버리면 다시 쓰고 싶을 때 클럭 신호를 공급하고 그 블럭을 초기화할 필요가 있습니다. 이 초기화에는 일정 시간이 소요되기에, 특정 명령을 실행할 때 필요한 블럭이 대기 상태라면 재시작해야 하는 경우엔 레이턴시가 늘어나게 됩니다.

그래서 이 블럭이 곧 사용될 것이라고 판단되면 실제로 쓰이기 직전에 클럭 신호의 공급을 재개하고 초기화해야 합니다.

그렇기에 실제로는 단순하게 클럭 신호를 조절하는 스위치를 하나 넣는 것으로 끝나지 않고, 재가동에 필요한 초기화 회로나 어느 시점에서 클럭 신호의 공급을 재개할지 예측하는 회로도 블럭마다 넣어야 합니다.

이렇게 되면 블럭을 쪼개 치밀한 전력 절약이 가능하지만, 회로 규모가 늘어나는 것은 물론 어떤 단위로 분할하는 게 가장 효과적인지 시뮬레이션을 반복해서 측정할 필요가 있습니다. 당연히 회로 자체도 P6을 그대로 쓰지 못하고 거의 재설계에 가까운 작업을 해야 합니다.

시장을 석권한 펜티엄 M. 코어 시리즈로 이어지다

팀나 그 자체는 2000년 봄에 처음 공개됐는데 당시에 실제로 작동하는 다이까지 완성했으니까, 설계 팀의 대부분은 1999년 중순까지는 작업을 마치고 바로 바니아스의 작업을 시작했다고 보입니다. 그렇게 계산하면 바니아스가 출시될 때까지 4년 정도 걸린 셈입니다.

기존의 것을 전혀 쓰지 않고 새로 CPU를 개발하면 5년 정도는 필요하기에 4년이라면 꽤 짧아 보이지만 그래도 시간이 걸리긴 했습니다. 이는 역시 재설계가 힘들었기 때문에 그랬을 겁니다.

물론 바니아스에는 성능 개선을 위한 요소도 포함돼 있었습니다. 스케줄러 효율을 높이는 MicroOps Fusion, 스택 조작을 개선하는 Dedicated Stack Manager가 바로 그것입니다. 또 분기 예측의 정확도도 펜티엄 3에 비해 많이 개선됐다고 합니다.

다만 이것은 IPC(Inter Process Communication)을 높이는 것이 아니라 오히려 같은 IPC를 더 낮은 전력으로 실현할 수 있게 됐다는 것이며, 최대 성능 자체가 개선된 것은 아니었습니다.

다만 그래도 바니아스가 펜티엄 M이란 이름으로 등장하면서 시장에서 폭발적으로 팔리게 됐습니다. 특히 노트북 분야에서의 약진이 두드러졌으며 이와 함께 시작된 센트리노(Centrino) 브랜드는 시장을 석권하게 됐습니다.

센트리노 로고. 인텔은 모바일리티의 전진을 나타낸다고 설명합니다.

노트북 시장에선 트랜스메타(Transmeta)가 크루소(Crusoe)를 2000년에 출시했습니다. 당황한 인텔이 펜티엄 3 기반으로 ULV(Ultra Low Voltage)인 제품을 출시하기도 했으나 이는 한계까지 전압을 떨어트려 전력을 낮춘 것이기에 당연히 성능도 떨어졌습니다.

그런데 펜티엄 M은 처음부터 전력을 절약하기 위해 설계된 것이기에, 소비 전력이 같으면 작동 클럭이 높아 성능에서 개선도 확실하게 이룰 수 있었습니다.

절대적인 성능에서 같은 클럭으로 작동하는 펜티엄 3와 별로 달라지진 않았지만, 그래도 2세대에선 90nm 공정을 사용한 도선(Dothan)이 최대 2.26GHz까지 클럭을 내 줬습니다.

도썬 코어의 펜티엄 M

이쯤 되니 데스크탑용 펜티엄 4나 그 경쟁상대인 애슬론 64와 거의 호각의 성능을 낼 수 있게 됐으며, 이를 노리고 조립 시장에서 펜티엄 M 메인보드가 유통되거나, 데스크탑용 소켓 478에 펜티엄 M을 탑재할 수 있는 어댑터가 등장에 시장에서 꽤 인기를 누렸습니다.

소켓 478 메인보드에 펜티엄 M을 장착할 수 있는 ASUS의 소켓 어댑터 CT-479

mPGA478 소켓에 CT-479를 장착. 478 소켓의 CPU 고정 레버를 그대로 CT-479를 고정하는데 씁니다.

이 성공에 힘입어 인텔은 P4 아키텍처 이후 펜티엄 M의 연장선상에 있는 제품을 출시하기로 결단했습니다. 이것은 2004년에 테자스(Tejas)를 취소하고 P4 아키텍처가 더 이상 답이 보이지 않게 된 것과 무관하지 않습니다.

펜티엄 M 아키텍처는 SSE2를 지원하지만 그 다음은 아니었고, 또 프레스컷 코어에서 도입했던 64비트도 지원하지 않았습니다. 모바일 뿐이라면 상관이 없으나 데스크탑이나 서버까지 시장을 확대한다면 이는 치명적인 단점입니다.

그래서 2006년에는 요나(Yonah) 코어를 출시했습니다. 이는 65nm로 이행한 것과 동시에 듀얼코어화한 것입니다. 여기에 공유 L2 캐시 등의 시스템을 채택했는데, 사실 네이티브 듀얼코어 제품으로 시장에 먼저 출시했던 애슬론 64 X2와 경쟁할 물건은 아니었고, 그저 코어의 성능을 확장하는 데 필요한 시간을 벌기 위한 수단이었습니다.

요나 코어를 쓴 코어 듀오

그리고 이 요나 코어로 약간의 시간을 번 사이에 내부를 64비트화함과 동시에 IPC를 높인 콘로(Conroe)의 개발을 추진합니다. 이것이 바로 코어 2란 이름으로 출시됐던 것입니다.

앞에서도 말한대로 펜티엄 4/D 이후에 펜티엄이란 브랜드는 단종됐으며, 요나 코어는 코어 듀오란 브랜드로 바뀌었으니 그런 의미에서 펜티엄은 바니아스/도선 코어가 마지막이라 할 수 있겠습니다.

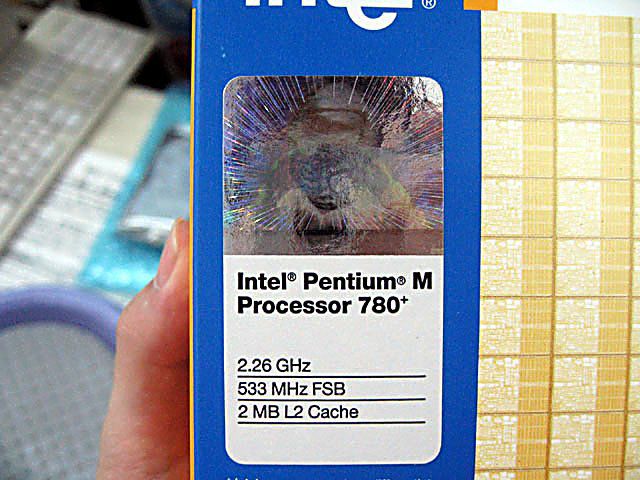

이렇게 완전히 사라질 것 같았던 펜티엄이란 브랜드를 마지막으로 지탱해 줬던 것이 펜티엄 M이라고 볼 수 있겠습니다. 2005년 7월에 출시된 펜티엄 M 780(2.26GHz, XDbit 지원) 펜티엄 M에선 마지막 제품입니다.

펜티엄 M 최상위 모델인 펜티엄 M 780

코어 2 시리즈 전성기에 부활한 펜티엄

펜티엄 4/D에서 코어 2로 이행

앞서 이야기한 펜티엄 M은 지원 메인보드가 약간 있긴 했으나 기본적으로는 모바일을 위한 물건이었습니다. 여기서 중요한 건 펜티엄 4와 펜티엄 D였지만, 인기가 별로 없다보니 제품 라인이 급속히 줄어들게 됩니다.

펜티엄 4부터 펜티엄 D까지의 인텔 CPU 로드맵

마지막으로 출시된 펜티엄 4는 펜티엄 4 HT 631/641/651/661로 2006년 4월에 나온 것입니다. 이들 제품은 2006년 1월 1일에 나왔는데 리비전 B1에서 리비전 C1으로 바뀐 것도 바로 이 때의 일입니다.

지금가지 나온 인텔 제품을 확인할 수 있는 웹 사이트인 http://ark.intel.com/를 보면 리비전 C1 다음에 리비전 D0이 라인업됐으며, TDP가 86W에서 65W로 줄어드는 변화가 있었으나 이게 실제 시장 출시로 이어졌는지는 확실치 않습니다.

한편 펜티엄 D는 바로 이 리비전 D0 제품이 2006~2007년까지 조금씩 출시됐으며 2007년 1월에 출시된 펜티엄 D 935가 마지막 제품이었습니다. 다만 이에 앞서 2006년 7월에 콘로 기반의 코어 2 익스트림 X6800이, 2006년 8월에는 코어 2 듀오 E6300/6400/6600/6700가 발매됐지요.

2006년 7월 27일에 출시된 코어 2 익스트림 X6800. 코어 2 듀오 시리즈와 다른 점은 클럭과 TDP입니다.

2006년 8월 5일에 출시된 코어 2 듀오 E6300/6400/6600/6700

코어 2 듀오는 기존의 LGA 775 소켓을 계승했기에 바이오스 업데이트하만 하면 기존의 펜티엄 4/D용 메인보드에서도 그대로 사용할 수 있었습니다. 소비 전력이 낮고 성능이 높아 급격하게 펜티엄 4/D를 대체했습니다.

당시 셀러론에선 프레스컷/시더밀 기반 코어가 계속 쓰였기에 시장에서 갑자기 P4 아키텍처가 없어진 것은 아니지만, 제품으로서 펜티엄 4/D는 2007년 중순에 아주 조감만 남아 있었고 2008년이 되기 전에는 유통 재고 외에 볼 수 없는 존재가 됐습니다.

그럼 펜티엄 브랜드가 이렇게 없어졌을까요? 그건 아닙니다. 펜티엄 듀얼 코어라는 이름으로 새로운 코어가 출시됐는데요. 여기에는 다수 특수한 사정이 있습니다.

L2 캐시를 콘로의 1/4로 줄인 듀얼코어 CPU, 펜티엄 듀얼코어

펜티엄 듀얼코어는 셀러론과 코어 2 사이의 틈을 메꾸기 위함

코어 2 세대에선 크게 나눠서 2종류의 코어가 있었습니다. 65nm 세대에서는 콘로(Conroe)와 앨런데일(Allendale), 45nm 세대에서는 펜린(Penryn)과 펜린-3M(Penryn-3M) 입니다.

두 제품의 차이는 L2 캐시의 용량입니다. 콘론/앨런데일이 4MB와 2MB, 펜린/펜린-3M이 6MB/3MB입니다. 허나 물리적인 다이 자체는 같으며 그저 L2 캐시를 절반 막아둔 것입니다. 이 외에도 FSB를 낮게 줄이는 등 성능 차이가 존재했습니다.

다만 이 두 제품은 코어 2 듀오에 속하는 모델 번호를 바꿔-그 뒤를 이어 나왔을 뿐입니다. 그리고 이것이 기존의 펜티엄 4/펜티엄 D를 대체하는 형태로 메인스트림 시장에 나왔습니다.

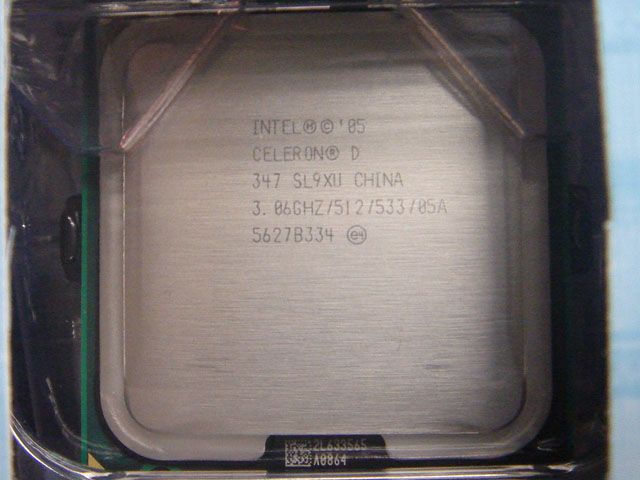

한편으로 보급형 셀러론은 2006년 5월에 시더밀-512K 기반 셀러론 D 347이 막 나왔고, 2007년에는 리비전 D0 코어를 사용한 셀러론 D 365가 나왔습니다.

시더밀-V 코어를 쓴 셀러론 D 347

2006~2007년에 콘로의 생산이 수요를 맞추지 못한 반면 시더밀 코어는 재고가 있었기에, 콘로 코어는 가격이 비싼 코어 2에만 출시했고 셀러론은 시더밀 코어로 충당할 예정이었던 듯 합니다.

이 계산이 무너진 것은 콘로 기반의 코어 2와 시더밀 코어의 셀러론 사이에 매우 큰 성능 차이가 있었고, 여기에 따른 AMD의 반격 때문이었습니다.

AMD는 2007년 11월에 출시한 페넘이 별 인기를 보지 못했으나 그 이전 모델인 애슬론 64 X2/애슬론 X2는 인기가 좋았습니다. 성능은 코어 2에 뒤졌지만 그만큼 가격을 인하했기에 가격 대 성능비로선 여전히 인텔의 유력한 경쟁자였습니다.

또 셈프론의 제품 라인업은 썩 신통치 않았으나 그 대신 싱글코어 애슬론 64/애슬론이 셀러론을 넘어서는 성능을 냈기에, 시더밀-512K 코어만으로 경쟁하기엔 힘들었습니다.

재밌는 건 인텔이 당시에 셀러론은 무조건 싱글 코어/싱글 스레드라는 원칙을 무너뜨리지 않았다는 것입니다. 지금 보면 시더밀-512K에서 하이퍼스레딩을 쓰면 경쟁력이 있지 않았을까 생각도 들지만, 그렇게 셀러론 라인의 성능을 향상시키는 건 인텔이 바라던 바가 아니었습니다.

그 대신 나온 아이디어가 셀러론과 코어 2 사이에 또 다른 제품 라인을 하나 끼운다는 것인데, 그렇게 태어난 브랜드가 펜티엄 듀얼 코어입니다.

코어 듀오의 전성기때 부활한 펜티엄

사실 펜티엄 듀얼코어 제품이 먼저 출시된 건 모바일이며, 그 기반은 코어 2가 나오기 전에 있었던 요나 기반의 코어 듀오입니다.

펜티엄 M 시대의 모바일 CPU 로드맵

다행이라고 해야 하겠는데 모바일에선 소비 전력이 많아 펜티엄 4가 거의 쓰이지 않았고, 모바일 펜티엄 3를 거쳐 펜티엄 M이 쓰이면서 최소한 모바일에선 펜티엄이란 브랜드가 그리 훼손되지 않았습니다.

다만 데스크탑의 이미지가 나빴던 것도 있어 요나 세대에서 고급형은 코어 브랜드의 코어 듀오로 바뀌었으며, 요나 코어를 그대로 쓴 펜티엄 T2060이 2007년 1월에 시장 출시됐습니다.

뒤이어 콘로 세대에서는 애런데일의 L2 캐시를 반으로 또 줄인 애런데일-1M이란 코어를 쓰는 펜티엄 E2140/2160이 2007년 6월에 출시됐습니다. 따라서 소매 시장에선 펜티엄 4/D를 대체하는 형태로 펜티엄 듀얼코어가 유통을 시작했습니다.

펜티엄 E2140/2160이 2007년 6월 3일에 출시

이 펜티엄 듀얼코어가 유통을 시작했을 때 65nm 공정에서 시더밀의 생산은 거의 끝났고 다소 여유가 생겼던 때입니다. 그래서 펜티엄 듀얼코어, 그리고 셀러론을 위해 인텔은 다이 차별화를 시작합니다.

콘로 코어는 143mm2의 다이 크기가 나오는데 아래 이미지에서 볼 수 있듯이 다이의 절반은 L2 캐시가 차지합니다.

2006년 가을 IDF의 기조 강연 슬라이드. Pat Gelsinger의 슬라이드가 콘로의 다이로 시작했습니다.

당초엔 여러 다이를 나눌 여유가 없어 L2 캐시를 절반 정도 막는 것으로 제품을 분리했는데, 제품 라인업이 안정화되면서 L2 캐시의 크기에 맞춰 여러 다이가 만들어져 원가 절감과 수율 개선으로 이어졌습니다.

그래서 애런데일과 애런데일-1M은 서로 다른 다이를 씁니다. 다이 크기는 각각 111mm2와 77mm2로 펜티엄 듀얼코어에는 77mm2의 애런데일-1M을 썼습니다.

2008년에 코어 2는 45nm 공정으로 이행하는 펜린으로 전환하며 펜티엄 듀얼 코어도 울프데일-3M(Wolfdale-3M0 기반으로 바뀝니다. 이것도 65nm 시절과 마찬가지로 처음에는 펜린의 L2 캐시를 일부 무효화해 출시한 후 이후에 전용 모델인 펜린-3M로 바뀌었습니다.

펜린 시절의 모바일 CPU 로드맵

펜린은 107mm2인데 비해 펜린-3M은 82mm2입니다. 코드네임에서 볼 수 있듯이 펜린-3M은 L2 캐시가 3MB이며 그 중 1MB를 무효화해 펜티엄 듀얼코어에 썼습니다.

펜린 코어는 107제곱mm인데 펜린-3M은 82제곱mm였습니다. 사진은 그냥 펜린.

펜린-3M은원래 코어 2 전용 칩입니다. 펜티엄 듀얼코어와 셀러론에 맞춰 L2 캐시를 더욱 줄인 다이를 만들지 않은 건 45nm 공정을 쓴 코어 i 시리즈로 데스크탑 네할렘(Nehalem)/린필드(Lynnfield)/헤븐데일(Havendal)을 개발할 필요가 있었기 때문입니다. 서버용으로는 Jasper Forest도 있었습니다.

이 정도로 수가 늘어나니 펜린 세대에선 이것저것 만들지 않고 단일 다이를 생산해 스펙을 바꾸는 게 효율적이 됐습니다. 게다가 2009년 초에 헤븐데일이 취소되고 클락데일(Clarkdale)로 전환되는 일이 있다보니 이 펜린-3M 기반 펜티엄 듀얼 코어는 꽤 길게 쓰이게 됩니다.

또 인텔은 코어 i에서 플랫폼을 바꿨습니다. 이것은 단순히 소켓이 바뀐 게 아니라 DDR2 메모리의 지원을 뺀 것으로 펜티엄 듀얼코어와 셀러론에선 구축 비용이 늘어나게 됐습니다.

또 코어 i 세대에서 칩셋의 구조가 바뀌면서 메모리 컨트롤러와 그래픽은 CPU에 통합하게 됐으나, 정작 그래픽 통합은 시기가 맞지 않아 1세대 코어 i 시리즈는 그래픽이 없는 제품 뿐이었습니다. 이것이 저가형인 펜티엄 듀얼 코어와 맞지 않은 것도 있고 해서 펜린-3M이 오래 쓰인 이유이기도 합니다.

가격대비 성능이 좋은 제품으로 브랜드를 재구축한 펜티엄

최종적으로 2010년이 되서야 클락데일 기반 펜티엄 G6950이 출시됐습니다. 다만 이 클락데일의 경우 CPU가 45nm, GPU가 32nm인 2개의 다이를 멀티 칩 모듈 구성으로 만들었기에 펜린-3M에 비해 꽤나 제조 원가가 높았다고 예상됩니다.

클락데일 시절의 인텔 CPU 로드맵

2011년 5월에는 샌디브릿지(Sandy Bridge) 기반 코어 i 시리즈가 등장하면서 펜티엄 G620/622/840/850이 출시됐습니다. 다이 크기는 1312mm니까 제조 원가는 다소 높았지만 멀티 모듈 구성인 클락데일보다는 쌌을 것입니다.

샌디브릿지 코어의 펜티엄 G 시리즈

코어 i 시리즈는 이어 22nm 공정인 아이비브릿지(Ivy Bridge)로 이행했다가 상당히 난항을 겪기도 했습니다. 펜티엄 듀얼코어로는 2012년 9월에 출시된 펜티엄 G2120이 첫 제품입니다.

사실 펜티엄 듀얼코어 같은 가격대에선 항상 22nm의 첨단 공정이 싸다고 볼 순 없어, 32nm 공정의 샌디브릿지를 꽤 오래 쓰기도 했습니다.

샌디브릿지부터 아이비브릿지까지의 인텔 CPU 로드맵

그리고 2013년에 코어 i3 시리즈는 4세대인 하스웰(Haswell) 기반으로 바뀌며 이에 따라 펜티엄 듀얼코어에도 하스웰 기반 제품이 다소 늦은 2013년 9월에 추가됐습니다.

20주년에 맞춰 등장한 Pentium Anniversary Edition

또 베이트레일-D(Bay Trail-D) 역시 펜티엄이란 이름츠로 출시돼 갑자기 제품 라인업이 늘어나게 됐습니다. 그 중 하나가 2014년 6월에 출시된 펜티엄 G3258입니다.

펜티엄 20주년 기념 모델로 2014년 6월에 출시된 펜티엄 G3258

펜티엄 G3258은 배수락이 해제돼 오버클럭하기 좋고 가격도 저렴해 인기가 좋았습니다. 이 모델의 목적은 펜티엄 20주년을 기념해 이제 한풀 꺾인 데스크탑에 활기를 가져오는 기폭제라 할 수 있겠습니다.

또 한가지. 펜티엄 4 이후 코어 시리즈 아래에 위치하는 자가형 제품이란 브랜드가 됐으나, 이를 가격 대비 성능이 좋은 제품이란 브랜드로 재구축하겠다는 의도가 이 20주년 기념 모델에 담겨져 있다고 할 수도 있겠습니다.

그렇다면 앞으로도 인텔은 펜티엄이라는 브랜드를 유지하면서 가격 대 성능이 높은 제품을 출시하지 않을까 기대해 봅니다.

소스

http://ascii.jp/elem/000/000/915/915669/

http://ascii.jp/elem/000/000/916/916624/

http://ascii.jp/elem/000/000/919/919669/

http://ascii.jp/elem/000/000/922/922066/

http://ascii.jp/elem/000/000/923/923273/

좀 옛날예기를 보면 일반 데스크탑에 들어가는 x86은 CISC고 IBM/SUN등이 미는 서버용 CPU가 RISC긴 했는데, 이건 그냥 기존 dos/ windows등의 호환성을 위해 x86을 쓰던 컨슈머용 pc 시장과 호환성보단 성능을 중시하던 서버 시장의 차이였고 지금은 완전 옛날 이야기가 되었습니다. (둘다 있긴 한데 당시에도 생각보다 점유율이 높진 않았고 지금은 x86 점유율이 완전 압도하고 있죠.. 이제 ARM이 어떻게 다시 들어가보려고 하는 참이고요.)

임베디드나 모바일쪽에서는 오히려 RISC가 압도하는 중이고요. ARM이나 MIPS같은 물건들..

리스크에서 속도 이득을 취하려면 전제가 맞아야 되는데... 설계가 맞는 곳에 넣는거지 정해진 방식은 없어요.

흔한 x86프로세서가 cisc방식을 쓰는데, 말씀하신대로 인스트럭션 파이프라인에서 나눠서 risc적으로 처리하는 방식을 동시에 취하기도 합니다.

마치 2000년대 중반의 터치패드에서의 감압식vs정전식 논란이랑 비슷한데 지금은 명백하게도 정전식이 훨씬 유리한 것과 비슷한 이치입니다.

RISC가 어느정도 우위였는가 하면 이 방식이 알려진 이후로는 대부분의 신규 아키텍처가 RISC를 내세우게 되었습니다. 그리고 이 영향은 아직도 끈질기게 남아있기도 하고요.

물론 CISC는 20년 동안 마켓에서의 선점효과에 의한 우위를 잃지 않았지만 모바일이 등장하면서 그것조차도 깨져버렸...

한때 팬티엄 브랜드를 폐기한다고 했다가(셀러론이였나요?) 다시 부활해서 다행이라고 생각하고 있습니다.

펜4 노스우드, 프레스캇은 직접 써봤네요..

도선할배는 아직도 신나게 갈....구다가 숨을 헐떡거리는거보고 어찌해야하나 고민중이고..

다시 돌고돌아 속칭 펜K까지...

아참, 펜4시절에 4Ghz 계획으로 따로 코드명이 테자스인가가 있었을겁니다. 당연히 프레스캇의 지옥의 불길에 타버린 계획이지만...

==> 제가 당시의 반도체 업계를 뒤흔들었던 그 유명한 팬티엄 FDIV버그 사건을 두고 '깔끔하게 수습'했다고 표현한 경우를 본 것은 원문 저자가 처음인 것 같네요. 처음부터 버그가 있는것을 알고 있는 상태에서 출시하고, 그게 유저에게 발각되어서 이슈화 되니까 몇달 동안 언플로 일관하다가 결국 당시 IBM같은 PC벤더들이 판금을 먹이는 초유의 사태까지 확대되었다가 말 그대로 백기들고 리콜에 배상금까지 지급해야만 했던, 인텔 기준에서도 창사 이래 최고 위기중 하나였던 사건을 두고 깔끔한 수습을 논해서는 안된다고 봅니다.

그게 깔끔한 수습이었다면 원자탄 두 방 얻어맞고 무조건항복한 태평양전쟁도 깔끔한 종전이라고 표현해야 할 판....

인텔이 깔끔하게 수습한 사건은 FDIV사건 이후 2년 후인가 터져나온 유사 사건입니다. 그때는 2년전 사건의 교훈을 살려 재빠르게 리콜하고 사과하면서 수습했지요.

==> 이건 펜티엄4가 아니라 펜티엄2~3때의 i820칩셋 MTH버그, 속칭 카미노게이트 이야기입니다.

http://www.thg.ru/blurb/20000510/print.html

필로땅사주세요

필로땅사주세요

좀더 일찍 넣을껄 그랬나봐요(?)